1

# Dynamic Models of Multilevel Converters by using the Power Oriented Graph Technique

Roberto Zanasi and Stefania Cuoghi

Abstract—The advances in power electronics, and new needs in renewable energy sources lead the multilevel converters to be advantageous compared to 2-level converters. Since modeling tools can be helpful to design new converter topology, this paper presents the dynamic models of the three basic topologies of multilevel converters: the Diode-Clamped, the Flying-Capacitor and the Cascaded H-Bridge converters. These models have been obtained by using the Power Oriented Graph (POG) technique, that is easy to be employed and implemented in Matlab-Simulink® environment. The proposed models are suitable to simulate high frequency sliding mode control and can be easily modified to model hybrid topologies. Simulation results confirm the validity of the presented models.

${\it Index Terms} {\it --} {\it Modeling technique, multilevel converters, power control.}$

# I. INTRODUCTION

In recent years, the research interest on multilevel converters has been increasing, leading to a rapid development of new topologies and control strategies, [1]-[4]. In particular, the advances in power electronics and new emerging needs in renewable energy systems and smart grid applications make the use of multilevel converters a promising alternative to classical 2-level converters, [5]-[6]. The main advantages are related to low total harmonic distortion (THD), low voltage stress of power switching devices and a namely low reduction of voltage derivative, reducing the filter dimension and increasing the system efficiency and power conversion, [7]-[8]. For these characteristics the multilevel converters are particularly interesting for high power applications. Moreover they are suitable for Photovoltaic (PV) systems, since the modularity of the PV arrays provides different DC voltage levels as direct sources of the converter, see [9].

In this continuously evolving scenario, modeling tools can be helpful to manufactures to reduce the time and the cost of the design of new topologies and control strategies. However the libraries of commercial tools are not always updated to the recent architectures. Moreover the high frequency of the PWM control signals make many of these tools inadequate to the simulation. In this paper the dynamic model of some basic multilevel converter topologies obtained by using the so called Power Oriented Graph (POG) modeling technique will be presented. This technique was introduced in 1991, see [10]-[12], and it is based on the same energetic approach

R. Zanasi and S. Cuoghi are with the Faculty of Engi-DII-Information Engineering Department, University of Modena and Reggio Emilia Via Vignolese 41100, Modena, Italy, e-mails: roberto.zanasi@unimore.it stefania.cuoghi@unimore.it.

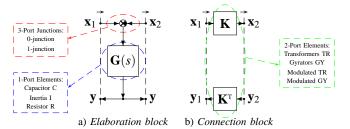

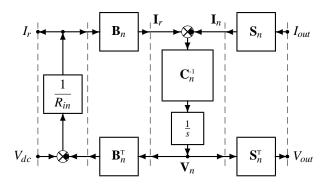

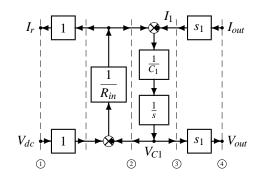

Fig. 1. POG basic blocks: elaboration block and connection block.

firstly introduced by H.M. Paynter in 1960 and used in the Bond Graph technique. One of the main advantage of the POG technique is its easy implementation in Matlab-Simulink® environment. In power electronic contest, the POG technique has been employed to model a grid connected photovoltaic system, see [13]-[15]. In particular the POG models of a dual active-bridge DC/DC converter and a single phase H-Bridge DC/AC converter have been introduced and simulated. In this paper the POG models of multilevel converters will introduced for the first time. In particular, the dynamic models of three basic kinds of multilevel topologies will be presented: the Diode-Clamped topology [16], the Flying-Capacitor topology [17]-[18] and the Cascaded H-Bridge topology [19]-[20]. The state-space equations of these topologies can be easily obtained by the models and used to design new control strategies.

Simulation results have been obtained in Matlab-Simulink® environment by using three types of PWM modulation algorithms: the Phase Disposition PWM (PD-PWM), the Phase Opposition Disposition PWM (POD-PWM) and the Alternate Phase Opposition Disposition PWM (APOD-PWM) algorithms, [9].

The paper is organized as follows. In Sec. II the Power Oriented Graphs modeling technique is presented. In Sec. III, IV and V the models of Diode-Clamped, Flying-Capacitor and Cascaded H-Bridge topologies are presented. Simulations results and conclusions end the paper.

# II. THE POWER-ORIENTED GRAPHS (POG) TECHNIQUE

The POG is a graphical modeling technique based on the same energetic approach of the Bound Graph (BG) technique, but it uses a different graphical notation. The two POG basic blocks are the elaboration block and the connection block, see Fig. 1. The first is used for modeling all the physical elements that can store and/or dissipate energy, while the second is used for modeling all the physical elements that transform the power without losses. The elaboration block corresponds to the 1-port element in BG technique (capacitor, inertia,

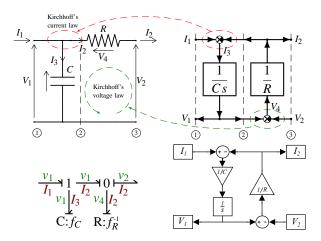

Fig. 2. Electrical circuit of CR filter, corresponding POG model, BG model and Matlab/Simulink® scheme.

resistor), while the sum element at the top of the elaboration block corresponds to the 3-port BG connection elements (0-junctions or 1-junctions). The connection block denotes all the 2-port elements of the BG technique: transformer, gyrators, modulated transformer and modulated gyrators. The dashed lines in Fig. 1 denote the power sections which connect the POG blocks to the external world. The scalar product  $\mathbf{x}^{\mathsf{T}}\mathbf{y}$  of the two *power vectors*  $\mathbf{x}$  and  $\mathbf{y}$  involved in each dashed line of a POG scheme, have the physical meaning of *the power flowing through that particular section*, see Fig. 1.

Let us consider the simple electrical example of the CR filter shown in Fig. 2. The corresponding POG model is shown on the top right, while the BG model is shown on the bottom left of the figure. Both the techniques provide the exact mathematical model of the system. While the BG scheme is quite compact, the POG model is easy to use, easy to understand and can be directly implemented in Matlab-Simulink® environment, see the block scheme on the bottom right of Fig. 2.

### III. POG MODEL OF DIODE-CLAMPED CONVERTER

First in this section the POG model of a 3-level Diode-Clamped or Neutral Point Clamped (NPC) converter will be described and then this model will be extended to n-level NPC converters.

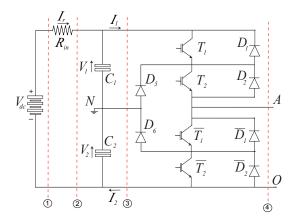

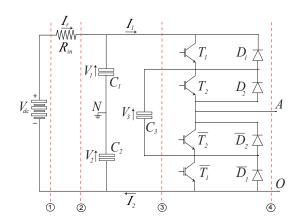

Fig. 3. Three-level Diode-Clamped converter scheme.

| $T_1$ | <i>T</i> <sub>2</sub> | $\overline{T_1}$ | $\overline{T_2}$ | $V_{AN}$    | $V_{AO}$   |

|-------|-----------------------|------------------|------------------|-------------|------------|

| 1     | 1                     | 0                | 0                | $V_{dc}/2$  | $V_{dc}$   |

| 0     | 1                     | 1                | 0                | 0           | $V_{dc}/2$ |

| 0     | 0                     | 1                | 1                | $-V_{dc}/2$ | 0          |

TABLE I CONTROL SIGNALS  $T_i$  AND OUTPUT VOLTAGES  $V_{AN}$  AND  $V_{AO}$  IN THE CASE OF 3-LEVEL DIODE-CLAMPED CONVERTER.

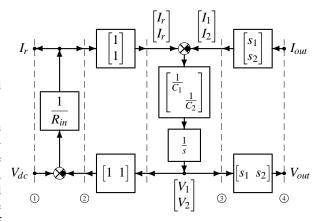

Fig. 4. POG model of 3-level Diode-Clamped Converter.

The classical electrical scheme of 3-level Diode-Clamped converter is shown in Fig. 3, while the corresponding POG dynamic model is given in Fig. 4. The first block present between sections ① and ② describes the model of the input resistance  $R_{in}$ . The connection and elaboration blocks present between sections ② and ③ represent the model of the input capacitors  $C_1$  and  $C_2$ , those dynamical equations can be written as

$$V_1 = \frac{1}{C_1 s} (I_r - I_1),$$

$V_2 = \frac{1}{C_2 s} (I_r - I_2).$

Referring to sections ③ and ④ of Fig. 3, let  $T_i = \{T_1, T_2, \overline{T_1}, \overline{T_2}\}$  denote the control signals of the transistors. The state 0/1 of  $T_i$  denotes the state OFF/ON of the corresponding transistor. The waveforms of  $T_i$  are generated by the control system such to connect  $C_1$  and/or  $C_2$  to the output. The three-levels of output voltages  $V_{AO}$  and  $V_{AN}$  are shown in Tab. I and their control can be obtained by different PWM modulation techniques, see [9]. The corresponding POG model is represented by the connection blocks between the corresponding sections in Fig. 4. In particular, the switching control signals  $s_1$  and  $s_2$  have been determined neglecting the dissipative losses of the converter and by using the relations between signals  $T_i$  and the output voltages  $V_{out} = V_{AO}$  and  $V_{out} = V_{AN}$  described as follows

$$V_{AO} = \begin{bmatrix} T_1 & T_2 \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \end{bmatrix} = \begin{bmatrix} s_1 & s_2 \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \end{bmatrix},$$

$$V_{AN} = \begin{bmatrix} T_1 & \overline{T_2} \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \end{bmatrix} = \begin{bmatrix} s_1 & s_2 \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \end{bmatrix}.$$

(1)

Fig. 5. POG model of m-level Diode-Clamped and Flying-Capacitor converters.

| $T_1$ | $T_2$ | $T_3$ | $T_4$ | $V_{AN}$    | $V_{AO}$    |

|-------|-------|-------|-------|-------------|-------------|

| 1     | 1     | 1     | 1     | $V_{dc}/2$  | $V_{dc}$    |

| 0     | 1     | 1     | 1     | $V_{dc}/4$  | $3V_{dc}/4$ |

| 0     | 0     | 1     | 1     | 0           | $V_{dc}/2$  |

| 0     | 0     | 0     | 0     | $-V_{dc}/4$ | $V_{dc}/4$  |

| 0     | 0     | 0     | 0     | $-V_{dc}/2$ | 0           |

TABLE II CONTROL SIGNALS  $T_i$  AND OUTPUT VOLTAGES IN THE CASE OF A 5-LEVEL DIODE-CLAMPED CONVERTER.

The state-space equations of the converter are the following

$$\begin{bmatrix} C_1 & 0 \\ 0 & C_2 \end{bmatrix} \begin{bmatrix} \dot{V}_1 \\ \dot{V}_2 \end{bmatrix} = \begin{bmatrix} -\frac{1}{R_{in}} & 0 \\ 0 & -\frac{1}{R_{in}} \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \end{bmatrix} - \begin{bmatrix} s_1 \\ s_2 \end{bmatrix} I_{out} + \begin{bmatrix} \frac{1}{R_{in}} \\ \frac{1}{R_{in}} \end{bmatrix} V_{dc}. \tag{2}$$

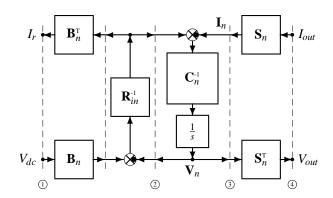

The extension of the POG model to m-level NPC converter is shown in Fig. 5, where vectors  $\mathbf{B}_n$ ,  $\mathbf{S}_n$  and matrix  $\mathbf{C}_n$  are defined as follows

$$\mathbf{B}_n = \begin{bmatrix} 1 \\ 1 \\ \vdots \\ 1 \end{bmatrix}, \quad \mathbf{S}_n = \begin{bmatrix} s_1 \\ s_2 \\ \vdots \\ s_n \end{bmatrix}, \quad \mathbf{C}_n = \begin{bmatrix} C_1 \\ C_2 \\ \vdots \\ C_n \end{bmatrix},$$

where n = m - 1. In particular the vector  $\mathbf{S}_n$  is a function of the desired output voltage  $V_{out}$

$$\begin{cases} \mathbf{S}_n = [T_1, T_2, ..., T_n]^{\mathsf{T}} & \text{if} \quad V_{out} = V_{AO}, \\ \mathbf{S}_n = [T_1, ..., T_{\frac{n}{2}}, -\overline{T_{\frac{n}{2}+1}}, ..., -\overline{T_n}]^{\mathsf{T}} & \text{if} \quad V_{out} = V_{AN}. \end{cases}$$

In the case of a 5-level converter the relationships between control signals  $T_i$  and the output voltages  $V_{AO}$  and  $V_{AN}$  are shown in Tab. II. In this case it is  $\mathbf{S}_n = [T_1, T_2, T_3, T_4]$  when  $V_{out} = V_{AO}$  and  $\mathbf{S}_n = [T_1, T_2, -\overline{T_3}, -\overline{T_4}]$  when  $V_{out} = V_{AN}$ .

# IV. POG MODEL OF FLYING-CAPACITOR CONVERTER

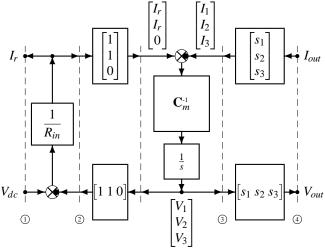

The electrical scheme of a 3-level Flying-Capacitor converter is shown in Fig. 6. The relations between the admissible configurations of control signals  $T_i$  and the corresponding values of the output voltages  $V_{AN}$  and  $V_{A0}$  are shown in Tab. III. The corresponding POG model is shown in Fig. 7, where  $C_m$  is a diagonal matrix with the values of capacitors  $C_1, C_2, C_3$  in

Fig. 6. Electrical scheme of 3-level Flying-Capacitor converter.

| $T_1$ | $T_2$ | $\overline{T_1}$ | $\overline{T_2}$ | $V_{AN}$    | $V_{AO}$   |

|-------|-------|------------------|------------------|-------------|------------|

| 1     | 1     | 0                | 0                | $V_{dc}/2$  | $V_{dc}$   |

| 1     | 0     | 0                | 1                | 0           | $V_{dc}/2$ |

| 0     | 1     | 1                | 0                | 0           | $V_{dc}/2$ |

| 0     | 0     | 1                | 1                | $-V_{dc}/2$ | 0          |

TABLE III CONTROL SIGNALS  $T_i$  and output voltages in the case of 3-level Flying-Capacitor converter.

its diagonal. The switching signals  $s_1, s_2, s_3$  can be obtained by the input-output relationships shown in Tab. III as follows

$$\begin{cases} [s_1, s_2, s_3] = [T_1, T_1, \overline{T_1}T_2 - T_1\overline{T_2}] & \text{if } V_{out} = V_{AO} \\ [s_1, s_2, s_3] = [T_1, -\overline{T_1}, \overline{T_1}T_2 - T_1\overline{T_2}] & \text{if } V_{out} = V_{AN} \end{cases}$$

Fig. 7. POG model of a 3-level Flying-Capacitor converter.

The state-space equations of 3-level Flying-Capacitor converter are the following

$$\begin{bmatrix} C_1 & 0 & 0 \\ 0 & C_2 & 0 \\ 0 & 0 & C_3 \end{bmatrix} \begin{bmatrix} \dot{V}_1 \\ \dot{V}_2 \\ \dot{V}_3 \end{bmatrix} = \begin{bmatrix} -\frac{1}{R_{in}} & 0 & 0 \\ 0 & -\frac{1}{R_{in}} & 0 \\ 0 & 0 & 0 \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \\ V_2 \end{bmatrix} - \begin{bmatrix} s_1 \\ s_2 \\ s_3 \end{bmatrix} I_{out} + \begin{bmatrix} \frac{1}{R_{in}} \\ \frac{1}{R_{in}} \\ 0 \end{bmatrix} V_{dc}.$$

(3)

The POG model of the Flying-Capacitor converter generalized to the *m*-level case is still represented by the POG scheme

shown in Fig. 5. In this case it is n = m,  $\mathbf{B}_n = [1 \ 1 \ 0 \ 0 \ \dots]^T$ , while  $\mathbf{C}_n$  is a *m*-dimensional diagonal matrix characterized by the values of the equivalent capacities of each branch of the circuit. The state space equations of the converter are the following

$$\begin{bmatrix} C_1 & 0 & 0 & \dots & 0 \\ 0 & C_2 & 0 & \dots & 0 \\ \hline 0 & 0 & C_3 \dots & 0 \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ 0 & 0 & 0 & \dots & C_n \end{bmatrix} \begin{bmatrix} \dot{V}_1 \\ \dot{V}_2 \\ \dot{V}_3 \\ \vdots \\ \dot{V}_n \end{bmatrix} = \begin{bmatrix} -\frac{1}{R_{in}} & 0 & 0 & \dots & 0 \\ 0 & -\frac{1}{R_{in}} & 0 & \dots & 0 \\ \hline 0 & 0 & 0 & \dots & 0 \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ 0 & 0 & 0 & \dots & 0 \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \\ V_3 \\ \vdots \\ V_n \end{bmatrix} \begin{bmatrix} S_1 \\ S_2 \\ \overline{S}_3 \\ \vdots \\ S_n \end{bmatrix} I_0$$

$$+ \begin{bmatrix} \frac{1}{R_{in}} \\ \overline{R}_{in} \\ 0 \\ \vdots \\ 0 \end{bmatrix} V_{dc}, \qquad I_r = - \begin{bmatrix} \frac{1}{R_{in}} & \frac{1}{R_{in}} & 0 & \dots & 0 \\ \overline{R}_{in} & \overline{R}_{in} & 0 & \dots & 0 \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \\ \overline{V}_3 \\ \vdots \\ V_m \end{bmatrix} + \frac{1}{R_{in}} V_{dc}.$$

In the case of a 5-level converter the control signals  $s_i$  have the following expression

$$[s_1, s_2, s_3, s_4, s_5] = [T_1, T_1, \overline{T_1}T_2 - T_1\overline{T_2}, \overline{T_2}T_3 - T_2\overline{T_3}, \overline{T_3}T_4 - T_3\overline{T_4}]$$

when  $V_{out} = V_{AO}$  and the expression

$$[s_1, s_2, s_3, s_4, s_5] = [T_1, \overline{T_1}, \overline{T_1}T_2 - T_1\overline{T_2}, \overline{T_2}T_3 - T_2\overline{T_3}, \overline{T_3}T_4 - T_3\overline{T_4}]$$

when  $V_{out} = V_{AN}$ .

### V. POG MODEL OF CASCADED H-BRIDGE CONVERTER

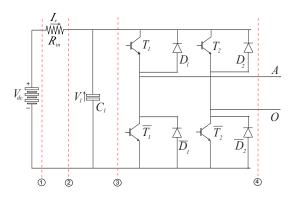

A 3-level Cascaded H-Bridge converter is a single H-Bridge converter represented in Fig. 8. The relationships between control signals  $T_i$  and the output voltage  $V_{out} = V_{AO}$  are described in Tab. IV, the corresponding POG model is shown in Fig. 9. It can be easily shown that in this case the switching control signal is  $s_1 = \overline{T_2}T_1 - T_2\overline{T_1}$ .

Fig. 8. Electrical scheme of 3-level Cascaded H-Bridge converter.

| $T_1$ | $T_2$ | $\overline{T_1}$ | $\overline{T_2}$ | $V_{AO}$  |

|-------|-------|------------------|------------------|-----------|

| 1     | 0     | 0                | 1                | $V_{dc}$  |

| 1     | 1     | 1                | 0                | 0         |

| 0     | 0     | 1                | 1                | 0         |

| 0     | 1     | 1                | 0                | $-V_{dc}$ |

TABLE IV CONTROL SIGNALS  $T_i$  AND OUTPUT VOLTAGE  $V_{AO}$  IN THE CASE OF 3-LEVEL CASCADED H-BRIDGE CONVERTER.

Fig. 9. POG dynamic model of a 3-level Cascaded H-Bridge converter.

The dynamic model of the generalized m-level Cascaded H-Bridge converter is represented by the POG block scheme shown in Fig. 10. In this case there is an input resistance  $R_{in}$  for each H-Bridge:  $\mathbf{R}_{in} = R_{in}\mathbf{I}_n$  where n = (m-1)/2. Vector  $\mathbf{B}_n$  is a n-dimensional column vector with all its component equal to 1. Matrix  $\mathbf{C}_n$  is a n-dimensional diagonal matrix with the values of the capacitors  $C_1, C_2, ..., C_n$  on its diagonal. The state space equations are the following

$$\begin{bmatrix} C_1 & 0 & \dots & 0 \\ 0 & C_2 & \dots & 0 \\ \vdots & \vdots & \ddots & \vdots \\ 0 & 0 & \dots & C_n \end{bmatrix} \begin{bmatrix} \dot{V}_1 \\ \dot{V}_2 \\ \vdots \\ \dot{V}_n \end{bmatrix} = \begin{bmatrix} -\frac{1}{R_{in}} & 0 & \dots & 0 \\ 0 & -\frac{1}{R_{in}} & \dots & 0 \\ \vdots & \vdots & \ddots & \vdots \\ 0 & 0 & \dots & -\frac{1}{R_{in}} \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \\ \vdots \\ V_n \end{bmatrix} - \begin{bmatrix} s_1 \\ s_2 \\ \vdots \\ s_n \end{bmatrix} I_{out} + \begin{bmatrix} \frac{1}{R_{in}} \\ \frac{1}{R_{in}} \\ \vdots \\ \frac{1}{R_{in}} \end{bmatrix} V_{dc}.$$

The vector  $\mathbf{S}_n$  of the control signals  $s_i$  is the following

$$\mathbf{S}_n = [\overline{T}_2 T_1 - T_2 \overline{T}_1, \ \overline{T}_4 T_3 - T_4 \overline{T}_3, \ ..., \ \overline{T}_{2n} T_{2n-1} - T_{2n} \overline{T}_{2n-1}]^{\mathsf{T}}$$

(4) in order to have  $V_{out} = V_{A0}$ .

Fig. 10. POG dynamic model of a m-level cascaded H-Bridge converter: n=(m-1)/2.

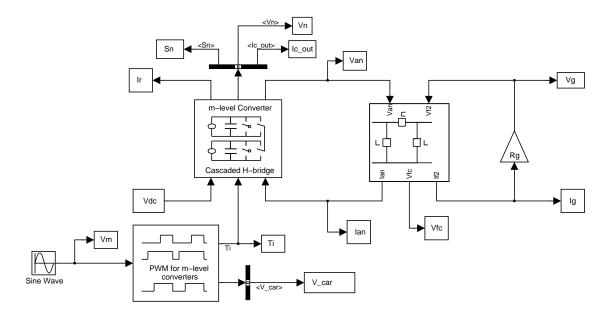

# VI. SIMULATION OF THE MODELS

The Matlab/Simulink® block scheme used to simulate the POG model of a Cascaded H-Bridge multilevel converter is shown in Fig. 11. In particular, the multilevel converter is controlled by the control signals  $T_i$  generated by a PWM subsystem which implements different types of modulation techniques (PD, POD and APOD) for a generic number m of voltage levels. The PWM subsystem has been designed to provide the control signals  $T_i$  for all the three types of multilevel converters presented in this paper. The Cascaded H-Bridge converter considered in Fig. 11 uses relation (4) to

Fig. 11. Matlab-Simulink® block scheme used to simulate the POG model of a cascaded H-Bridge multilevel converter.

generate the control vector  $S_n$  by signals  $T_i$ . The *LCL* filter present in the simulation scheme is used to reduce the high order harmonics introduced by the PWM modulation. The parameters for the filter are the following:  $C = 3 \mu F$ ,  $L_1 = 0.8$  mH,  $L_2 = 0.4$  mH,  $R_1 = 0.1 \Omega$  and  $R_2 = 0.05 \Omega$ . The POG model of the considered *LCL* filter is described in [13].

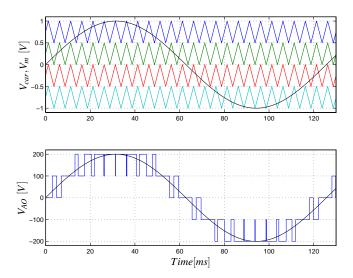

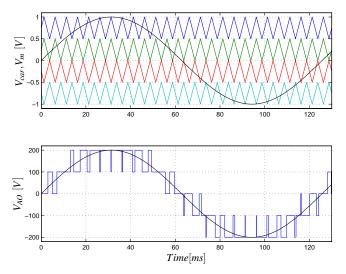

Fig. 12. Five-level Cascaded H-Bridge: PD triangular carriers  $V_{car}$ , modulation voltage  $V_m$  and output signal  $V_{AO}$ .

## A. Simulation results

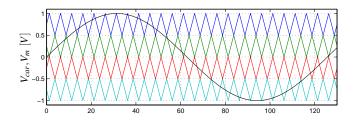

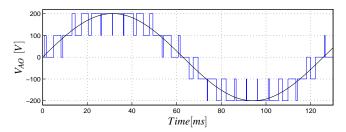

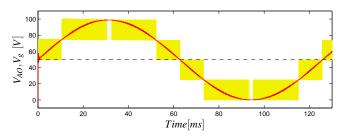

1) Cascaded H-Bridge converter: The considered 5-level Cascaded H-Bridge converter is characterized by the following parameters: PWM carrier frequency  $f_c=200$  Hz, modulation frequency  $f_g=50$  Hz, input voltage  $V_{dc}=100$  V, input resistance  $R_{in}=1$   $\Omega$ , output resistance  $R_g=50$   $\Omega$  and internal capacitors  $C_i=80$  mF. The waveforms of the triangular carriers  $V_{car}$ , the modulation voltage  $V_m$  and the output voltage  $V_{AN}$

Fig. 13. Five-level Cascaded H-Bridge: POD triangular carriers  $V_{car}$ , modulation voltage  $V_m$  and output signal  $V_{AO}$ .

are shown in Fig. 12, Fig. 13 and Fig. 14, respectively for the following three different types of PWM modulation: PD, POD and APOD. Notice that in this case the frequency of the PWM carrier has been chosen quite small in order to clearly show the different behaviors obtained with the three different types of PWM modulation.

2) Diode-Clamped converter: A 5-level Diode-Clamped converter has been considered. The following parameters have been used:  $V_{in}=100$  V, PWM carrier frequency  $f_c=17$  kHz and modulation frequency  $f_g=50$  Hz. The simulation results obtained using a PD-PWM modulation and when  $V_{out}=V_{AN}$  are shown in Fig. 15. Notice that in this case the considered PWM carrier frequency is high and the filtered output voltage  $V_g$  has a sinusoidal time behavior quite similar to the modulation voltage  $V_m$ .

Fig. 14. Five-level Cascaded H-Bridge: APOD triangular carriers  $V_{car}$ , modulation voltage  $V_m$  and output signal  $V_{AO}$ .

Fig. 15. Output voltage  $V_{AN}$  and filtered signal  $V_g$  of a 5-level Diode-Clamped converter obtained using a PD modulation.

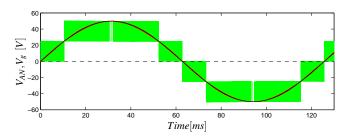

3) Flying-Capacitor converter: A 5-level Flying-Capacitor converter has been considered. The following parameters have been used:  $V_{in} = 100 \text{ V}$ , carrier frequency  $f_c = 17 \text{ kHz}$ , modulation frequency  $f_g = 50 \text{ Hz}$ . The simulation results obtained using a POD-PWM modulation and when  $V_{out} = V_{A0}$  are shown in Fig. 16.

# VII. CONCLUSION

In this paper the dynamic models of three different types of multilevel converters obtained using the Power Oriented Graphs technique have been presented. The simulation results confirm the validity of the proposed models. The POG dynamic models have the advantage to be easy to use, easy to understand and can be directly implemented and simulated

Fig. 16. Output voltage  $V_{AO}$  and filtered signal  $V_g$  of a 5-level Flying-Capacitor converter obtained using POD modulation.

in Matlab-Simulink® environment. Variants on the proposed POG models can be easily implemented and simulated in a very short time. For this reason the POG technique can be helpful to manufacturers to analyze and design new converter topologies.

### ACKNOWLEDGMENT

The authors would like to thank C. Tebaldi.

### REFERENCES

- [1] H. Akagi et al., A 6.6-kV Transformerless STATCOM Based on a Five-Level Diode-Clamped PWM Converter: System Design and Experimentation of a 200-V 10-kVA Laboratory Model, IEEE Transactions on Industry Applications, vol.44, no.2, pp.672-680, March-april 2008.

- [2] D. Floricau and F. Richardeau New Multilevel Converters Based on Stacked Commutation Cells With Shared Power Devices, IEEE Transactions on Industrial Electronics, vol.58, no.10, pp.4675-4682, Oct. 2011.

- [3] L. G. Franquelo, J. Rodriguez, J. I. Leon, S. Kouro, R. Portillo, and M. A. M. Prats, *The age of multilevel converters arrives*, IEEE Ind. Electron. Magazine, vol. 2, pp. 28-39, June 2008.

- [4] A.L. Batschauer, S.A. Mussa, M.L. Heldwein, *Three-Phase Hybrid Multilevel Inverter Based on Half-Bridge Modules*, IEEE Transactions on Industrial Electronics, vol.59, no.2, pp.668-678, Feb. 2012.

- [5] S.D.G. Jayasinghe, D.M. Vilathgamuwa and U.K. Madawala, A hybrid cascaded multilevel inverter with supercapacitor direct integration for wind power systems, IEEE 8th International Conference on Power Electronics and ECCE Asia (ICPE-ECCE), May 2011.

- [6] J. Rodriguez, S. Bernet, B. Wu, J.O. Pontt, and S. Kouro, Multilevel voltage-source-converter topologies for industrial medium-voltage drives, IEEE Trans. Ind. Electron., vol. 54, pp. 2930-2945, Dec. 2007.

- [7] L. Tan et al. An improved control method for PWM current source rectifier with active damping function, IEEE International Conference on Industrial Technology ICIT, 10-13 Feb. 2009.

- [8] J. Rodrguez, J. Lai, and F. Peng, Multilevel inverters: a survey of topologies, controls and applications, IEEE Trans. Ind. Electron., vol. 49, pp. 724-738, Aug. 2002.

- [9] J. Rodriguez et al. Multilevel Converters: An Enabling Technology for High-Power Applications, Proceedings of the IEEE, vol.97, no.11, pp.1786-1817, Nov. 2009.

- [10] R. Zanasi, Power Oriented Modelling of Dynamical System for Simulation, IMACS Symp. on Modelling and Control, Lille, France, May 1991

- [11] R. Zanasi, G. H. Geitner, A. Bouscayrol, W. Lhomme, Different energetic techniques for modelling traction drives, ELECTRIMACS 2008, Oubec, Canada, 8-11 June 2008.

- [12] R. Zanasi, The Power-Oriented Graphs technique: system modeling and basic properties, Vehicular Power and Propulsion Conference VPPC 2010, Lille, France, 1-3 September 2010.

- [13] R. Zanasi and S. Cuoghi, Power control of grid-connected photovoltaic systems, IEEE International Symposium on Industrial Electronics ISIE, Gdansk, Poland, 27-30 June 2011.

- [14] R. Zanasi and S. Cuoghi, Model of soft-switching converter and power control for smart grid applications, IEEE PES Innovative Smart Grid Technologies (ISGT) Asia Conference, Perth, Australia, 13-16 Nov. 2011.

- [15] R. Zanasi and S. Cuoghi, Model of Soft-Switching Converter and Power Control of Grid-Connected Photovoltaic Systems, IEEE Industrial Electronics Conference IECON, Melbourne, Australia, 7-10 Nov. 2011.

- [16] A. Nabae, et al., A new neutral-point-clamped PWM inverter, IEEE Transactions on Industry Applications, vol. IA-17, pp. 518-523, 1981.

- [17] T. A. Meynard, et al., Modeling of multilevel converters, IEEE Transactions on Industrial Electronics, vol. 44, pp. 356-364, 1997.

- [18] J. I. Leon, et al., Improving multilevel flying capacitor converters features using new voltage ratios definitions, Electrotechnical Conference MELECON 2006, IEEE Mediterranean 2006.

- [19] S. Anees Abu, et al., A new topology of capacitor-clamp cascade multilevel converters, Power Electronics and Motion Control Conference IPEMC 2006. CES/IEEE 5th International, 2006, pp. 1-5.

- [20] D. Kai, et al., A new diode-clamp cascade multilevel converter, Industrial Electronics Society IECON '03. The 29th Annual Conference of the IEEE, 2003.